【前言】

hello 大家好,提前祝大家劳动节快乐~ 今天钛叔给大家讲一讲放大器,啥? 放大器辣么简单的东西用得着你讲…… 嘿嘿,确实,钛叔不才,只能抛砖引玉(狗头脸)。今天要给大家讲的是斩波放大器,何为斩波放大器呢? 如果从事工业仪器仪表的童鞋应该了解的到,我们常常会涉及一些微弱信号的放大,一般是由传感器输出,这类信号的特点就是频率低、信号极其微弱极其敏感。如果我们要对其进行分析应用,就必须进行信号放大,这个时候放大器的基本性能参数就显得尤为关键。高输入阻抗、低输出阻抗、低温飘、低失调电压等等,才能保证稳定出色的信号放大,也是基于此,斩波放大器也就应运而生。今天要讲的型号就是ICL7650,该芯片是由 Intersil(英特矽尔)出品的(该公司已被被瑞萨收购了),下面大概讲一讲该芯片的一些特性。

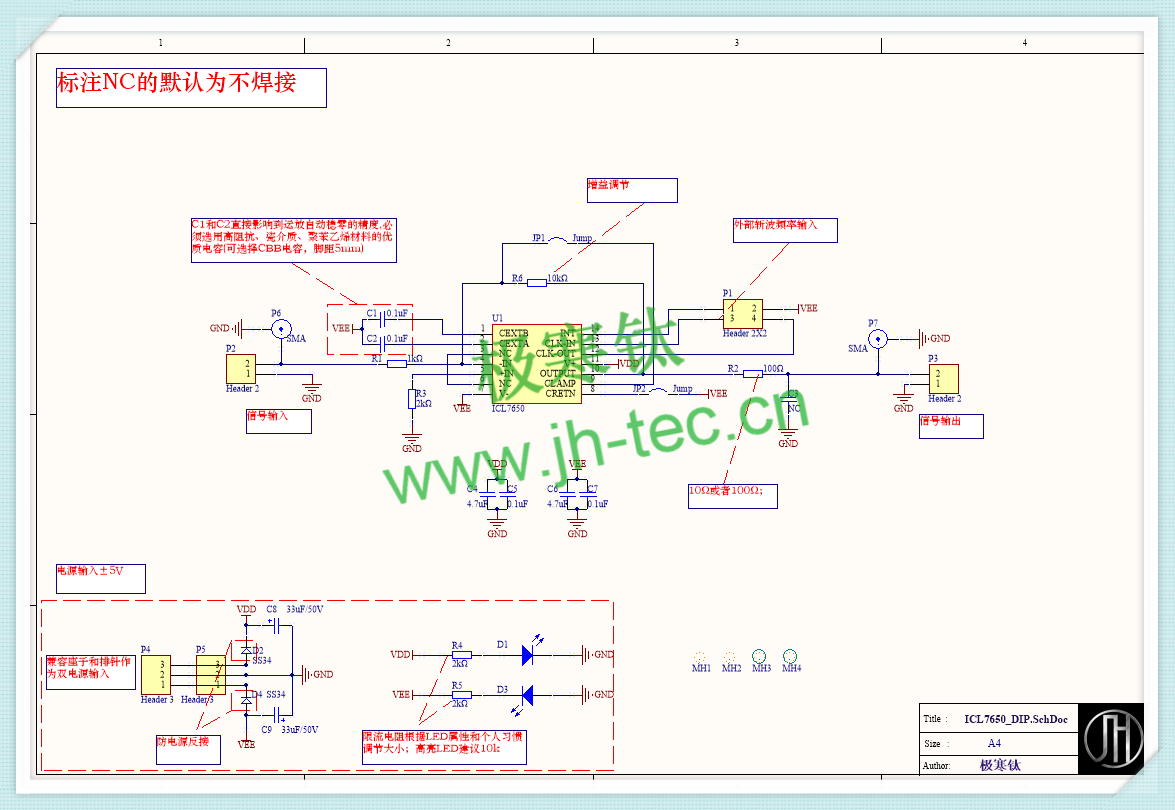

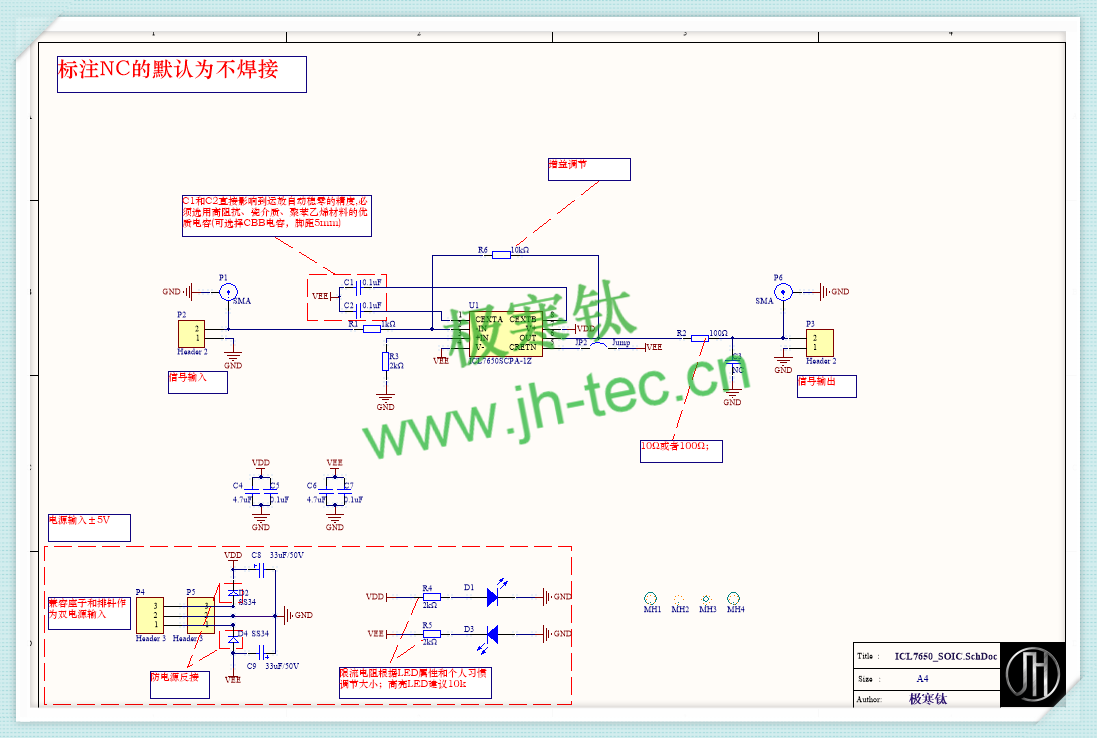

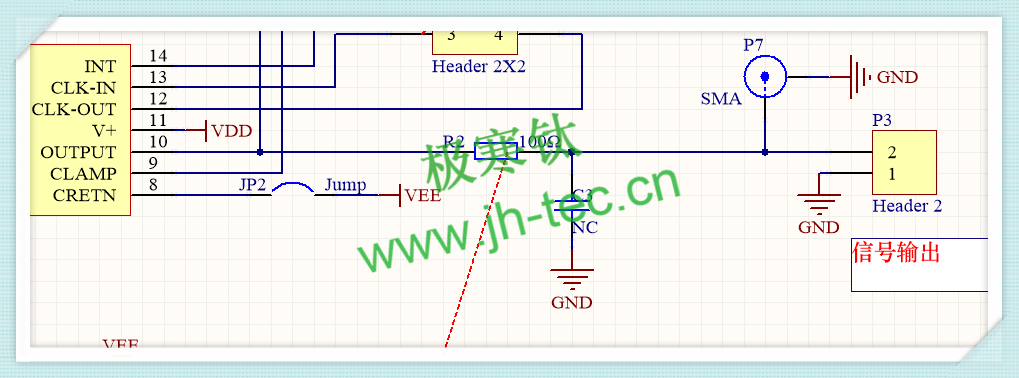

首先,ICL7650常用的有DIP-14和SOIC-8两种封装,钛哥把这两种都分别设计了一下,主要区别有哪些呢? DIP-14相比SOIC-8多了一个时钟选择,可通过INT/EXT引脚选择外部时钟(此管脚接VEE时候)或者内部时钟(此管脚悬空或者接VDD的时候),INT CLKOUT为时钟外部输入,EXT CLKIN为内部时钟输出。设计这个目的是针对有些场合对时钟精度要求比较高,就可以采用外部时钟输入。另外,DIP-14还具有OUT CLAMP引脚,该引脚为钳位输出,目的主要是防止因输出过载而导致放大器出现阻塞的现象(阻塞的意思就相当于把信号“隔断”,此时不再具备放大作用)。SOIC-8封装的不具备以上两个功能,大家可根据自己的实际应用需求选择。

【硬件电路设计】

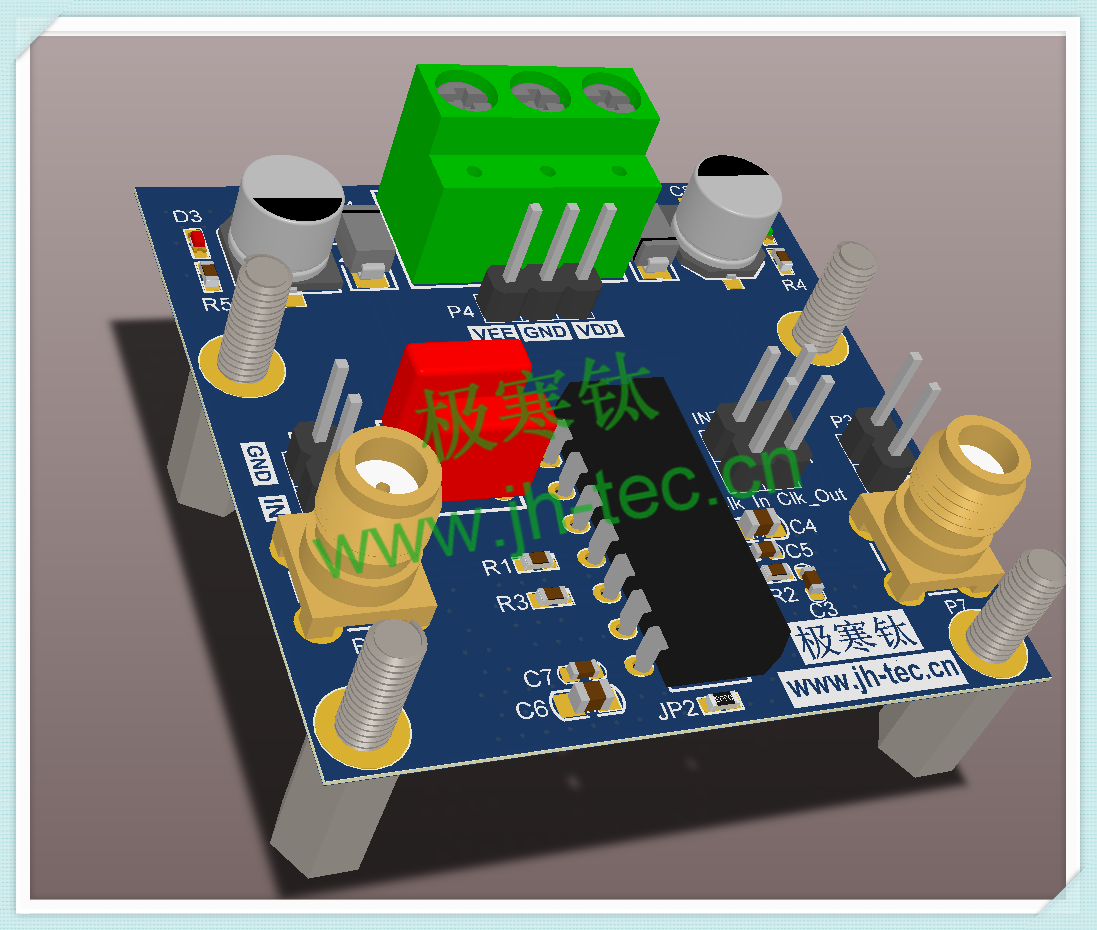

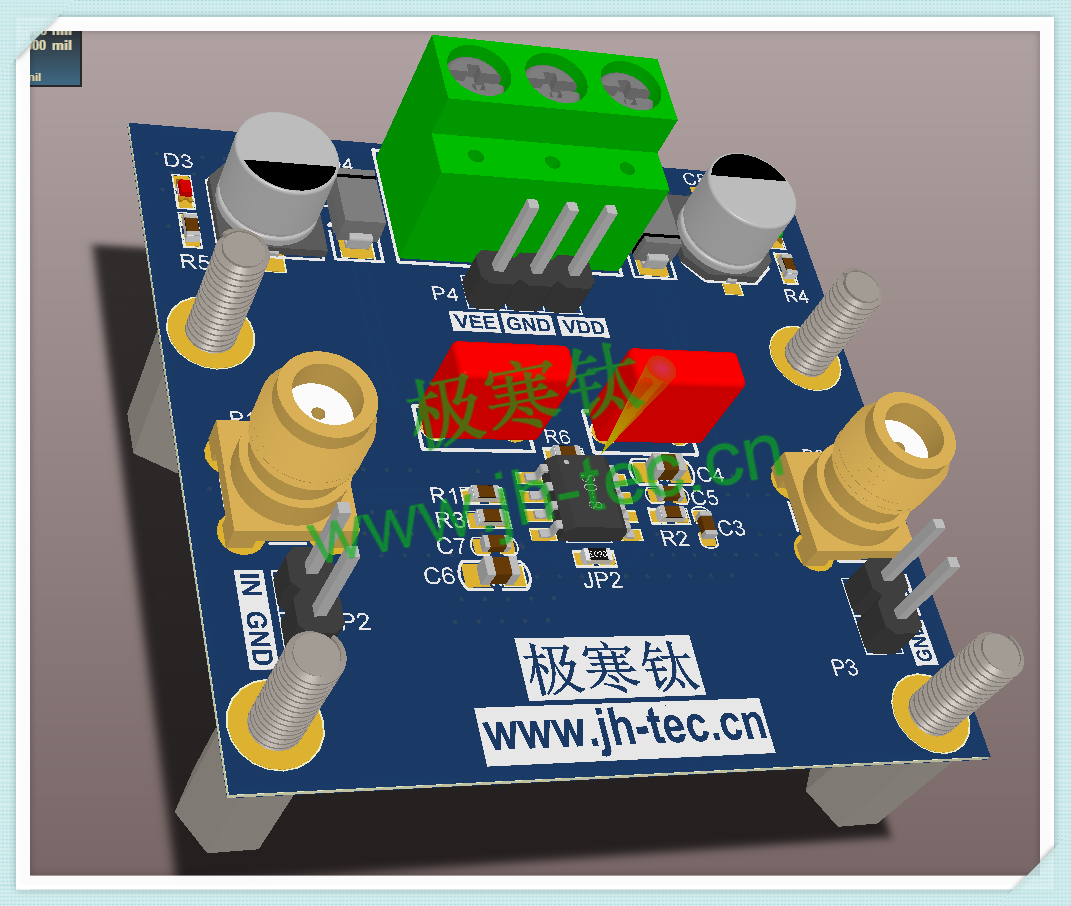

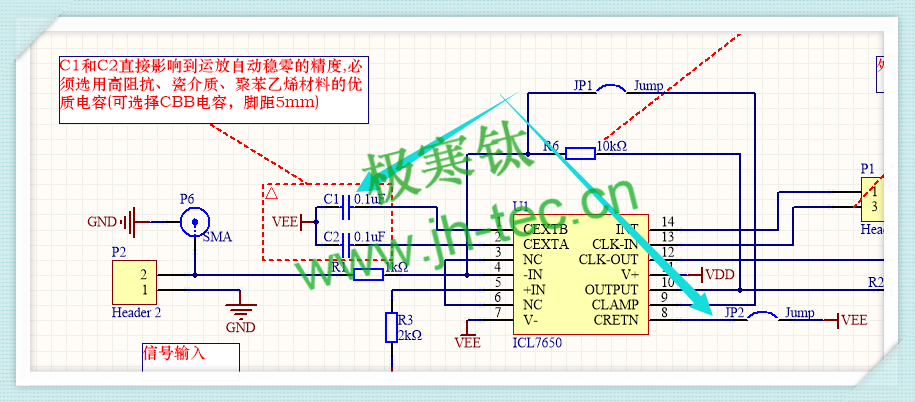

以下是钛哥的DIP-14和SOIC-8两部分的设计原理图和PCB,原理图上注明了相关设计注意事项,PCB元器件均采用3D封装,以方便配合结构设计,极寒钛附有原理图和PCB源文件哈。

DIP-14:

SOIC-8:

1、调零/记忆电容。这里先重点说一说该部分的设计,这两个电容CEXTB和CEXTA非常之重要,直接会影响到运放自动稳零的效果,因此这两个电容必须选择瓷介质、高阻抗、聚苯乙烯材料的优质电容,参数可用0.1uF。另外注意,电容另外一端的接法,钛哥这里是接到VEE,不是最优的处理方式,最好的处理方式是两个电容的一端采用独立屏蔽线接到CRETN(CEXTA 和 CEXTB 的公共端)然后再接到外部金属壳上,金属壳和板内GND通过一个大电阻和电容相连。以下是钛哥的简易处理方式,如果CEXTB和CEXTA接到VEE,CRETN就可接可不接了。

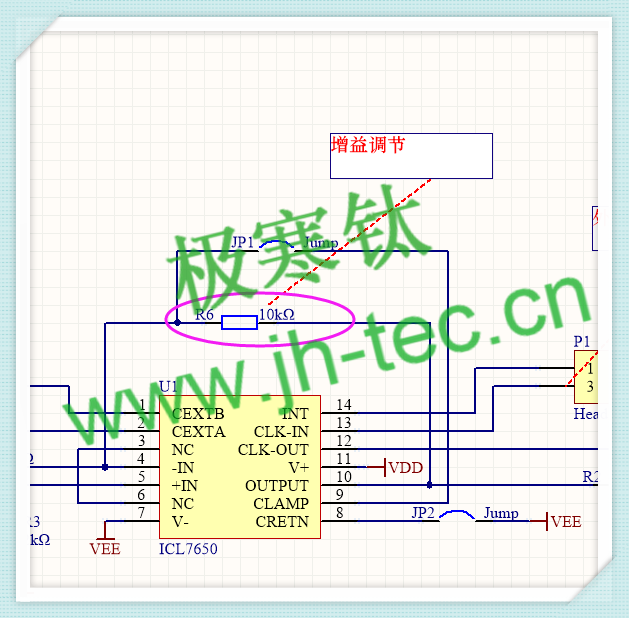

2、增益调节及钳位输出。调节反馈电阻可调节增益大小,有些童鞋喜欢用滑变作为反馈电阻来调节放大倍数,钛哥严重不建议养成这样的习惯,如果是低频信号可能问题不大,但是一旦高频信号,滑变的寄生参数是有可能导致放大器振荡!所以最好是采用固定电阻(不要说这里是低频可以采用,尽量不要养成这个习惯!); 钳位输出引脚可以参照下面钛哥的设计,用一个跳线连接输入,如果需要用到该功能就短路连接,反之即断开。

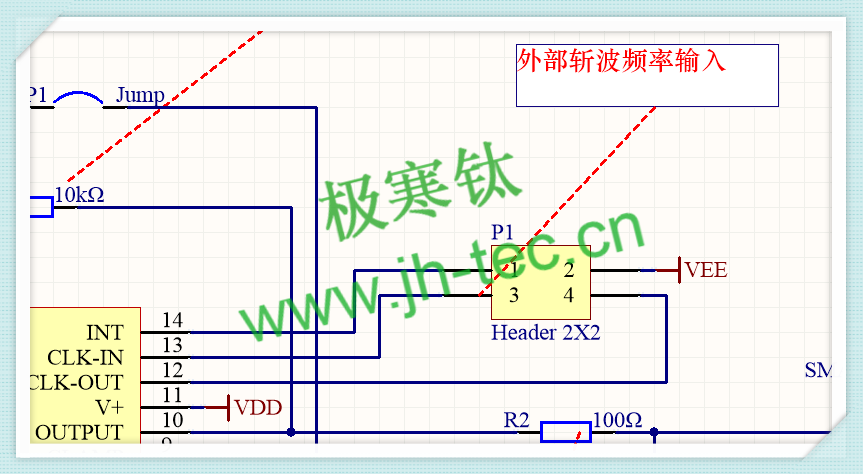

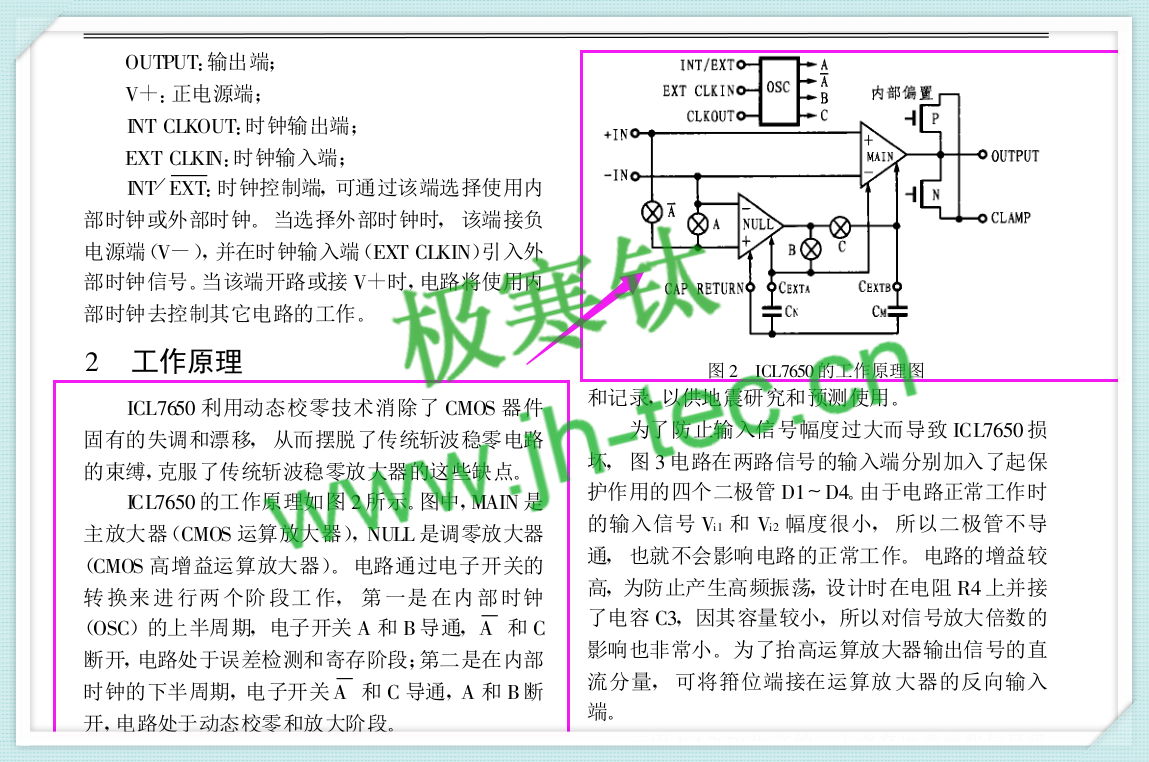

3、时钟电路。钛哥这里采用一个4pin的排针来设计,将内部输出时钟和外部输入时钟引脚引出,同时排针接VEE,如果大家需要使用外部时钟的时候,用跳线帽插上INT/EXT和VEE,同时输入时钟信号;如果使用内部时钟,则不插跳线帽。该部分的工作斩波工作原理可参考下面的截图。

4、信号输入输出。钛哥的接口处设计兼并了插针和SMA插座,考虑到方便调试,大家也可以借鉴哈。另外这里设计输出电阻的大小,可取值几十欧姆或者100Ω,该电阻主要是利于信号平滑输出。

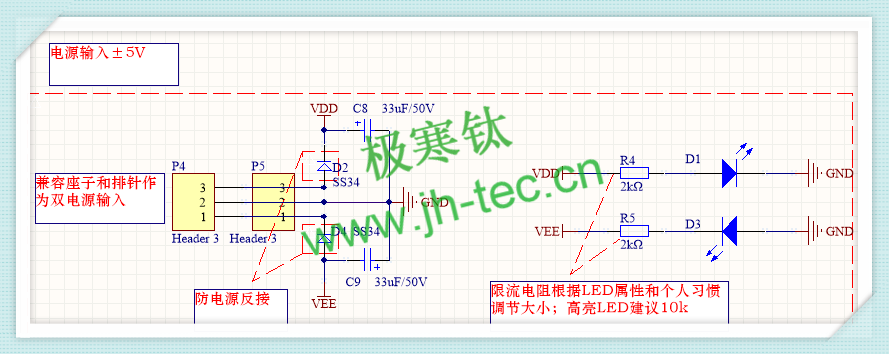

5、电源。钛哥这里没有设计稳压芯片,直接输入±5V给内部供电,注意保证电源的质量,从而保证放大器的工作效果。输入可以采用一个二极管防反接。输入电源可以兼并设计插针和插座,方便调试。

以下是设计源文件,仅供参考:

链接:https://pan.baidu.com/s/1ABb-BX8t2Lt5USMsu_SqbQ

提取码:nzlq