【轻松一刻】

青年向大师哭诉:“大师,我高考失利,考不上大学,父母责骂我,

女朋友也离我而去,请您收下我,让我皈依佛门吧!”

只见大师拿出一叠高考资料,

青年恍然大悟:“大师是叫我不要放弃高考,明年再战,是吗?”

大师摇头说道:“施主,我们这里只招本科以上,你还是先回去考上本科再过来面试吧!”

【进入正题】

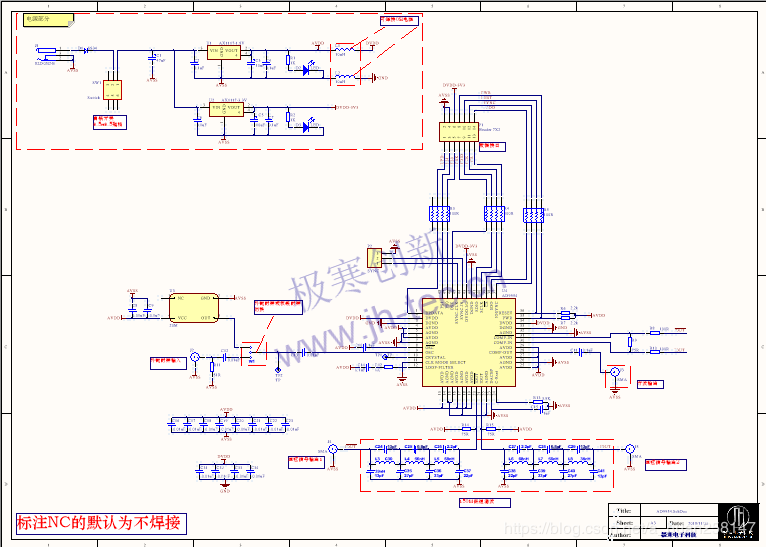

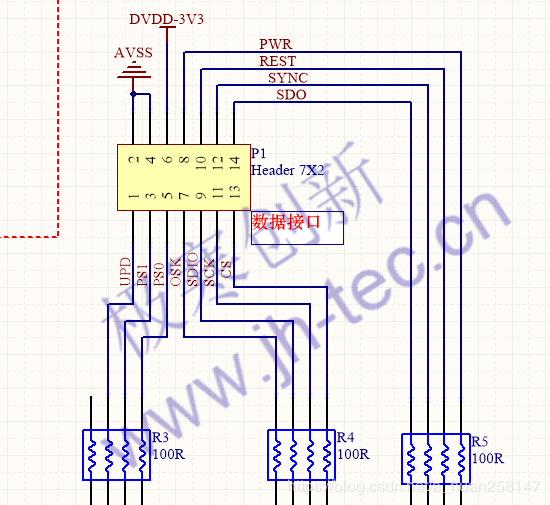

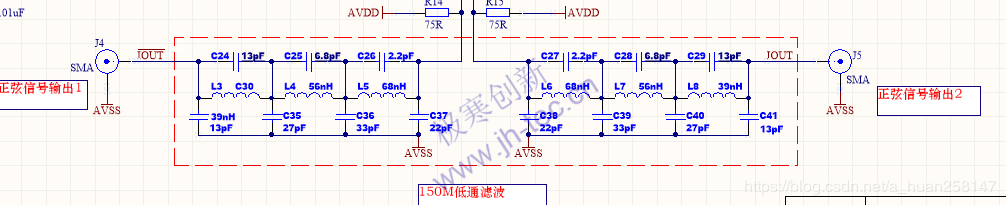

最近调试了AD9954模块,和大家分享一些经验,原理图如下,标注了相关的说明,方便后期读图,也方便调试的时候注意

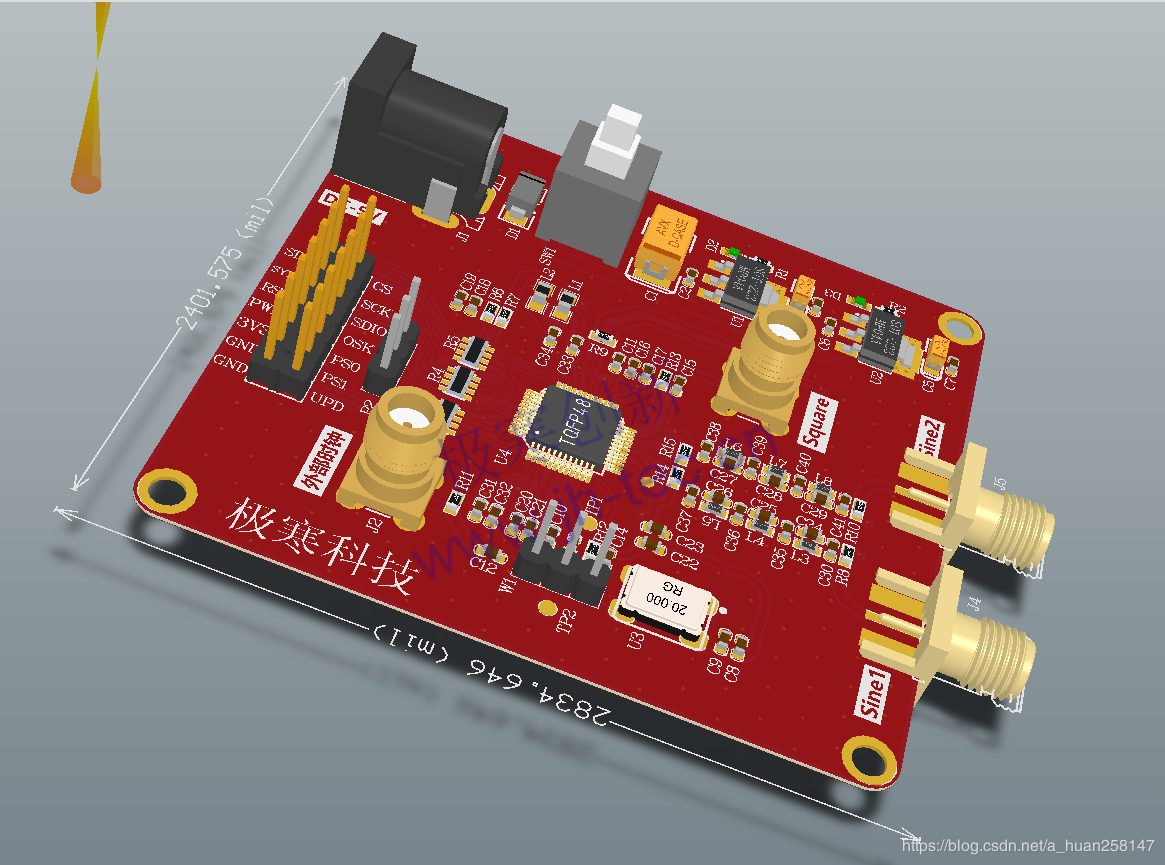

PCB如下,使用3D封装

芯片特点

- 400 MSPS内部时钟速度

- 集成14位DAC

- 可编程相位/幅度扰动

- 32位频率调谐精度14位相位调谐精度

- 相位噪声高于-120 dBc/Hz

- 出色的动态性能

- 窄带SFDR >80 dB

- 串行输入/输出(I/O)控制

- 超高速模拟比较器

- 自动线性和非线性频率扫描

- 4种频率/相位偏移形式

- 1.8 V电源

- 软件/硬件控制的断电功能

- 48引脚TQFP集成1024字×32位RAM

- 基于PLL的REFCLK乘法器

- 单晶体驱动的内部振荡器

- 相位调制功能

- 多器件同步

使用经验建议:

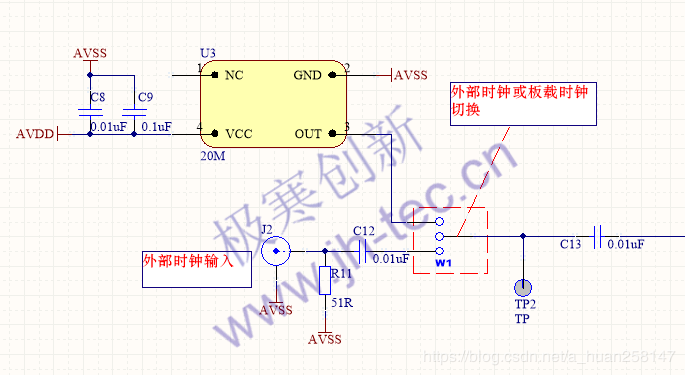

1.时钟设计,建议参照如下,备份SMA外部时钟源输入,板载晶振作为默认源,通过排针进行选择。注意设计此处PCB的时候应该尽量使时钟挨近芯片,减短走线长度。

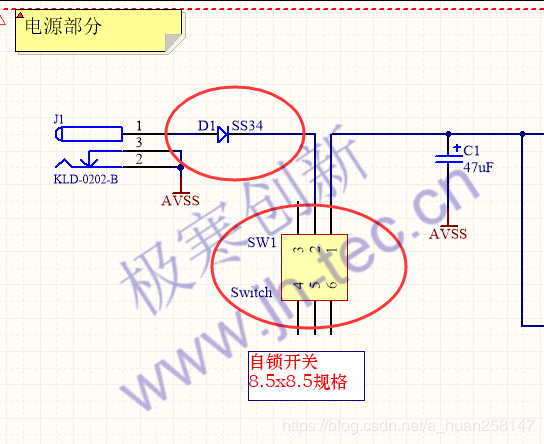

2.电源输入这里,建议增加一个防反接的二极管,毕竟这个芯片不便宜呀,开关使用自锁开关控制电源的关断。

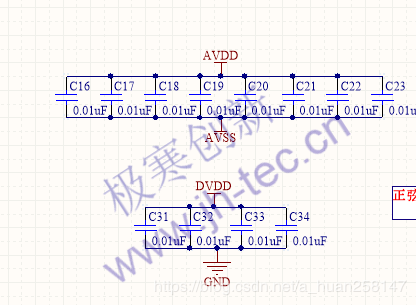

3.数字电源和模拟电源建议参照如下设计,单点相接的电感可以采用0Ω电阻替代。

H}`G632E.png)

4.数据通信这里的排阻值不应取太大,否则将影响正常通讯,最开始调试的时候我是采用1K,结果通信不成功,找了很久问题才发现是这个阻值太大造成,遂改为100Ω,也可以采用33Ω。

5.芯片的每处供电管脚部分都应加上退耦电容。

6.滤波电路部分布局布线的时候切记要紧凑,使走线尽量短。

下面是原理图和PCB源文件, 仅供学习交流

链接:https://pan.baidu.com/s/1wfcLX86WsgvNNVaw5UUP5A

提取码:wdih

© 著作权归作者所有